ISSN (e): 2250-3021, ISSN (p): 2278-8719

PP 32-36

# High Performance Flex Ray Communication Controller for Fpga -Based Automated System

# Merlin Metilda.G, B. Hemalatha 2

1 Pg Student, Dept Of Ece, Thirumalai Engineering College -Kanchipuram 2 Assistant Professor, Dept Of Ece, Thirumalai Engineering College -Kanchipuram

Abstract: In Recent Most Advanced Applications We Can Use The Benefit From Tight Coupling Of The Embedded Computing Units With The Communication Interface, Thereby Providing Functionality Beyond The Flex Ray Standard. Such An Approach Is Highly Suited To Implementation On Reconfigurable Architectures. In This Paper We Presents Highly Pipelined Fsm Based Flex Relay Protocol That Consists Of A Reconfigurable Processing Module, Including Reconfigurable Compute Units And Output Control Logic, Cam Memory Units, And Peripheral Circuits. Flex Ray Communication Controller (Cc) Which Integrates Configurable Extensions That Augment The Cc's Capabilities Beyond Those Defined By The Flex Ray Standard. The Main Core Comprises Of Protocol Engine (Pe) Which Implements The Protocol Behavior, And The Controller Host Interface (Chi) Which Interfaces To The Host Ecu. Here We Describe An Fpga-Based Communication Controller Which Features Configurable Extensions To Provide Functionality That Is Unavailable With Standard Implementations. Finally For Custom Interfacing Purposes Such As In Embedded Controller Applications Nios Ii Based System Build And Core Bus In-Between The Main Processor And The I/O Interface Are Used.

**Iindex Terms** — Functional Obfuscation, Hardware Security, High-Level Transformations, Intellectual Property (Ip) Protection, Obfuscation, Reconfigurable Design, Structural Obfuscation.

## I. Introduction

The Processor Design Highly Optimized (Area, Power & Speed) Electronic Zthrough Sopc Builder Based Hardware Synthesize And Verify The Functionality Through Modelism. Flex-Ray Is A New Communication Protocol Designed To Provide Large Bunches Of Data To Be Exchanged In Real-Time And With High Dependability Between Electronic Control Units (Ecu). It Features Data-Rates Up To 10 Mb/S. It Is Accounting For Both Time And Event Triggered Transmissions. (Beyond Can)[1] .The Host Checks Wakeup Event, Based On This Decides Modes Of Operation By State Will Be Next. In The Form Of Static Slots For Synchronous Time-Triggered Communication And Dynamic Slots For Burst Mode Event-Triggered (Priority Based) Data Transfer. In Modern Processor Widely Used Can Protocol For Internal Communication. Can Bus Speed 10mb/S And Operation Under Event Triggered Method. Area, Size And Power Requirement Is Large. Speed Is Limited (10mb/S) And Conflict Occur In Modes Of Operation. In This Paper, We Present An Architecture-Optimized Flex Ray Communication Controller (Cc) [4] Which Integrates Configurable Extensions That Augment The Cc's Capabilities Beyond Those Defined By The Flex-Ray Standard. The Controller Provides Enhancements To The Data Path, Like Programmable Width Time Stamping, Data Filtering, Header Insertion And Processing Functions, Which Are Abstracted Away From The Host Function. Our Flexible Architecture Can Be Used To Design Advanced Ecus On Reconfigurable Hardware That Consume Less Power And Offer Increased Consolidation, While Providing Enhanced Capabilities That Are Impossible To Implement Using Standard Controllers Or Ip Cores[2] We Also Quantify The Potential Of The Proposed Controller Using Case Studies Based On Existing And Evolving Automotive Applications That Are Safety-Critical And Data-Intensive, Our Experiments Show That Advanced Features Like High-Speed Mode Switching For Fault-Tolerant Ecus, Low Latency Data Handling For High Performance Gateways, Timeliness And Security For Messages Can Be Efficiently Achieved By Integrating Such Extensions Within The Controller Data Path Rather Than Offloading Them To The Processing Logic.

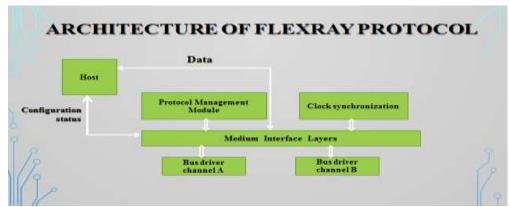

Figure 1 Architecture Of Fleray Protocol

#### II. Related Work

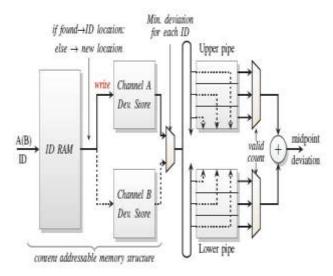

The Investigate The Scheduling Problem For The Dynamic Segment Of Flex-Ray. We Formulate A Nonlinear Integer Programming Problem (Nip) That Minimizes The Duration Of The Dynamic Segment. In Order To Obtain Efficient Schedules. While The Cc Independently Implements The Flex-Ray Protocol Services. The Chi[5] Of Each Node Contains A Buffer For Each Related Fid. The Host Implements A Periodic Scheduling Table (Pst) Per Allocated Fid. Each Node Consists Of A Host And A Communication Controller (Cc) That Is Connected By A Controller-Host Interface (Chi). While The Cc Independently Implements The Flex-Ray Protocol Services. An Arrow Indicates The Current Message To Be Transferred To The Respective Transmit Buffer In The Chi. The Flex-Ray Network Splits The Bus Into Separate Branches And Operates As A Selective Central Switch. The Proposed Device Is Increasing Both Available Bandwidth And Safety Of Existing Flex-Ray Networks. Schedule Execution (Se) Module Implements The Clock Synchronization Algorithm. Coding And Decoding (Codec) [4] Module Extracts Synchronization Information. The Mtg Stores The Current Micro- And Macro Tick And Updates The Time Base Accordingly .Measurement Of The Deviation Values And Calculation Of The Correction Values Is Done By The Clock Synchronization Process (Csp), Switched Flex-Ray Networks Use Star Coupler Called A Switch, Thereby Increasing The Effective Network Bandwidth, Branch Parallelism And Multiplexing Is Available. Safety-Critical In-Vehicle Electronic Control Units(Ecus) Demand High Levels Of Determinism And Isolation. It Uses Fpga Partial Reconfiguration And A Customized Bus Controller To Offer Fast Recovery From Faults. Results Show That Such An Integrated Design Is Better Than Alternatives That Use Discrete Bus Interface Modules. To An Increase In The Number Of Computational Nodes And The Need For Faster In-Vehicle Networks. The Predictability And Isolation Of Safetycritical Function Providing Both Static And Dynamic Flexibility With High Computational Capabilities At Lower Power Consumption. Fpgas Improve Upon Processor-Based Ecus By Providing Better Determinism And Segregation. The Customizable And Reconfigurable Nature Of The Fabric Can Be Exploited By Implementations Addressing A Wide Range Of Applications For Modern And Future In-Vehicle Systems. Non-Safety-Critical Applications Like Multimedia And Driver Assistance Can Leverage The High Computational Capability Of Fpgas [2] While Taking Advantage Of Dynamic Re-Configurability To Multiplex Functions. Fpgas Also Enable Techniques For Implementing Multiple Levels Of Fault-Tolerance And Redundancy To Support Fpga-Based Safety-Critical Ecus For The Drive Train And Drive-By-Wire Systems.

## III. Architecture Design

Flex-Ray Is A New Communication Protocol Designed To Provide Large Bunches Of Data To Be Exchanged In Real-Time. It Features Data-Rates Up To 10 Mb/S .It Is Accounting For Both Time And Event Triggered Transmissions.(Beyond Can). Much Work Has Been Done On Scheduling Communication On The Shared Bus. Optimizations Of The Static And Dynamic Segment Of The Flex-Ray Protocol Has Been Widely Addressed In Among Scheduling Algorithms And Provides A Comparison Between Optimization Strategies Like Simulated Annealing, Genetic, Hybrid-Genetic And Probabilistic Approaches Applied By Various Algorithms. Given A Set Of Communication Requirements, All Algorithms Try To Optimize The Number Of Communication Slots And Cycles That Are Required To Schedule The Different Messages, Satisfying All Requirements. The Optimization In Most Cases Is To Find The Minimum Number Of Communication Slots That Can Solve The Problem, Hence Consuming Minimum Bandwidth. Alternatively, The Problem Can Be Formulated To Maximize The Number Of Unused Slots, Which Provides Flexibility For Future Expansion.

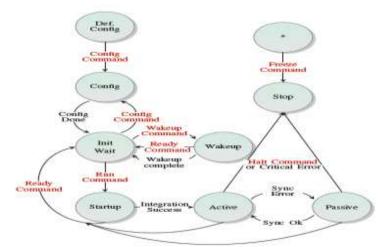

Figure 2 Flex-Ray Cc Modes

The Flex-Ray Cc Switches Between Different Operating States, Based On Network Conditions And/Or Host Commands, Ensuring Conditions Defined By The Flex-Ray Protocol Are Met At All Times. The Cc Architecture [5], As Shown In Fig. 3, Comprises The Protocol Engine (Pe) Which Implements The Protocol Behavior, And The Controller Host Interface (Chi) [3] Which Interfaces To The Host Ecu. The Chi Module Communicates With The Host And Handles Commands And Configuration Parameters For The Flex-Ray Node. These Parameters Are Defined For The Particular Cluster The Node Is Operating On, And Areinitialized During The Node's Configuration Phase. The Chi Feeds The Current State And Operational Status To The Host For Corrective Action If Necessary. There Are Transmit And Receive Buffers And Status Registers For The Data-Path To Isolate Control And Data Flow. The Chi May Also Incorporate Clock Domain Crossing Circuitry To Enable The Different Interfaces To Work In Distinct Clock Domains.

These Corrections Must Be Applied In The Same Way At All Nodes And Must Full Fill The Following Conditions: 1) Rate Correction Is Continuously Applied Over The Entire Cycle. 2) Offset Correction Is Applied Only During The Nit In An Odd Cycle And Must Finish Before The Start Of The Next Communication Cycle. 3) Rate Correction Is Computed Once Per Double Cycle, Following The Static Segment In An Odd Cycle. The Calculation Is Based On Values Measured In An Even-Odd Double Cycle. 4) Calculation Of Offset Correction Takes Place Every Cycle But Is Applied Only At The End Of Odd Cycle

It Has Pmm,Cs And Mil [4] For Major Constituent Part.Pmm Is To Control And Coordinate The Clock Synchronization And Medium Interface Layer. Macro And Micro Timer Are Synchronized By Use Of Clock Synchronization.Mil Uses Encoding And Decoding For Transmission. Through Hardware Synthesis Area , Power & Speed Of Pmm, Cs And Mil Modules Are Analyzed. Improve The Overall Throughput Rate. It Features Data-Rates Increase Up To 10 Mb/S. It Is Accounting For Both Static And Dynamic Transmissions.

Figure 3 Architecture Of Custom Flex-Ray Communication Controller

Give Configuration Command, States Moves To Wait Then Wakeup. Give Run Command From Wait State, Entire Process Will Done In Active State .If Synchronization Error Arises, It Will Moves To Passive And Critical Command In The State Of Halt Mode. Communication Controller Is Designed Using Finite State Machine (Fsm) [5] Methodology. Speed Is Independent Number Of States, And Depends Only On The Number Of Transitions Into A Particular State. Traditional Controllers Depend On The Host Processor To Read The Received Data And Determine The Usefulness Of It. The Controller Issues A Data Interrupt, To Which The Processor Responds With A Status Register Read Followed By A Data Read Request, Subsequently Receiving The Data. These Overheads Are Wasted In The Case Of Frames With Irrelevant Data (Like Obsolete Or Untimely Data) Or Multi-Cycle Data Frames Where The Processor Cannot Process The Received Fragment Until More Data Is Available. In The Case Of Critical Data Fraes Like Error State That Require Immediate Attention, The Latency Introduced By The Traditional Scheme Limits The Performance Of Safety Critical Systems Which Rely On Host-Triggered Recovery.

# **IV. Software Implementation Results**

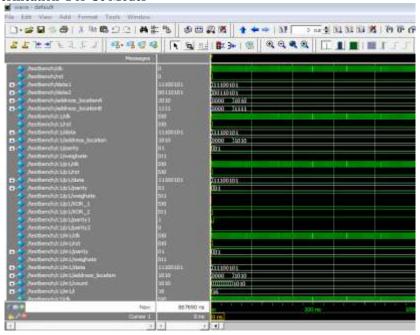

## A) Functional Verification For Cc Modes

# **B) Performance Of Slow Corner**

## C) Performance Of Area

Flow Summary Successful - Wed Sep 10 22:22:47 2014 Flow Status 9.0 Build 132 02/25/2009 SJ Web Edition Quartus II Version Revision Name QTOP Top-level Entity Name FLEX\_CC\_MODE Cyclone III Family EP3C16F484C6 Device Timing Models Final Met timing requirements N/A 46 / 15,408 ( < 1 % ) Total logic elements Total combinational functions 46 / 15,408 ( < 1 % ) 12 / 15,408 ( < 1 % ) Dedicated logic registers Total registers 12 Total pins 13 / 347 (4%) Total virtual pins 0 Total memory bits 0 / 516,096 (0%) Embedded Multiplier 9-bit elements 0 / 112 (0 %) Total PLLs 0/4(0%)

## V. Conculsion

In This Paper, We Have Given An Overview Of The Flex Ray Protocol And The Generic Architecture Of The Communication Controller, As Defined By The Specification. By Identifying And Extracting Operations Which Are Mutually Exclusive Or Natively Parallel, We Have Designed A Custom Controller Which Takes Advantage Of The Heterogeneous Resources On Modern Fpgas, Resulting In Reduced Logic Footprint, And Low Power Consumption, While Providing A Host Of Features Beyond Those Described By The Standard And To Give An Overview Of The Flex Ray Protocol And The Generic Architecture Of The Communication Controller To Reconfiguration To Provide Flexible

### References

- [1] S. Chakraborty, M. Lukasiewycz, C. Buckl, S. Fahmy, N. Chang, S. Park, Y.Kim, P. Leteinturier, And H. Adlkofer, "Embedded Systems And Software Challenges In Electric Vehicles," In Proc. Design, Automation And Test In Europe (Date) Conference, 2012.

- [2] S. Shreejith, S. A. Fahmy, And M. Lukasiewycz, "Reconfigurable Computing In Next-Generation Automotive Networks," Ieee Embedded Systems Letters, Vol. 5, No. 1, Pp. 12–15, 2013.

- [3] I. Sheikh, M. Hanif, And M. Short, "Improving Information Throughput And Transmission Predictability In Controller Area Networks," In Proc. International Symposium On Industrial Electronics (Isie). Ieee, 2010, Pp. 1736–1741.

- [4] J. K "Otz And S. Poledna., "Making Flexray A Reality In A Premium Car," In Proc. Of The Sae International, 2008. [5]. Flexray Communications System, Protocol Specification Version 2.1 Revision A, Flexray Consortium Std., December 2005.